Mips 1

역사적으로 중요한 의미를 가짐

예전에는 1 Chip 안에 들어가는 Transistor 개수가 exponential하게 증가했지만 아직 프로세서 전체를

1 chip에 구현할 정도는 아님

이 시점에는 이정도 transistor 개수는 single chip processor로 할수 있겠다

cisc에서 risc로 변화하는 시점임

risc architecture의 가장 중요한 요소는

- Pipelined execution

- Cache memory

나머지는 이 두개의 부가적인 느낌임

Mips는 일부 임베디드 에서 아직 사용중임

General Purpose Register 32개

흔히 범용 레지스터라고 부름

0번 레지스터는 항상 0을 지니고 있음

어찌 보면 Read Only Register라고 볼수 있음 아무리 다른 값 넣어도 0을 지니고 있음

예외를 만든 이유는 0을 많이 사용하기 때문이다

R format의 특징

Register 3개 지정 각각 5bit

shamt :얼마나 shift 하냐

마지막 funct 은 opcode의 확장

즉 opcode space가 더 넓다

I format

16상수와 Register 2개 필요

J format

jumpy에만 사용

addi $s1 $s2 100

I format이고 상수는 16bit인데 32bit로 확장할려고 하면

sign bit으로 앞 16개를 쭉 집어 넣어야 한다

signed 연산이기 때문에 overflow 발생 가능성 있다

overflow

양수 + 양수 or 음수 + 음수의 경우 발생 가능

subtract는 2개 밖에 없는 이유

subtract immediate는 add immediate를 음수로 주면 된다

16bit 밖에 안되기 때문에 나머지는 0으로 채워버림

shift left logical 왼쪽으로 밀고 0으로 채워버림

0111을 shift left 2 bits하면 1100이 된다

shift right는 두개가 있다

left의 경우 연산으로 생각하면 X 2인데

right shift는 %2이다

right shift logical은 밀고 0을 채워넣고

arithmetic은 0이 아닌 sign bit를 채워 넣는다

ex)

1000을 logical right 1bit하면 0100

arithmetic으로 하면 1100

load upper immediate

사실 load가 아님

lui $s1 40이면 처음에 40을 넣고 16 bit를 left shift한다

32 bit중 앞 16bit를 주어진 상수로 채우고 싶다

즉 실질적으로 memory load하는 것은 없다

store word

레지스터 안에있는 32bit를 지정된 주소로 쓰는 거다

halfword는 16bit

store byte 1 byte 저장

store float는 floating point에 있는 4 byte

swc1인데 c1의 의미는 coprocessor

coprocessor 0은 memory management unit(MMU)

1은 방금 사용한 floating point

load word

주소에서 지정된 4 byte채움

load halfword

signed로 하면 양수 음수 취급

채우는걸 sign bit로 하냐 마냐를 정하는 거다

load word는 꽉차서 sign bit 여유가 없다

ex)

lw $s1 21($2)가 있다고 하면

주소가 4의 배수 규칙을 지켰는지 안지켰는지 알고싶다면

$2의 값을 알아야 최종 주소를 알수 있다

즉 여기선 모른다

두가지 방식이 있다

network protocol에서 심각해진다

branch on equal 동일하면 L로 이동

opcode가 6bit이기 때문에 32bit를 지정할수가 없음

26bit만 남음

byte주소로 뒤는 00으로 끝남 그래서 생략

이제 28bit 확보

다음 4bit은 현재 Program counter에서 앞 4bit를 떼옴

즉 PC 4bit + 원래 26bit + 00

jump and link 돌아올 지점을 남겨둠

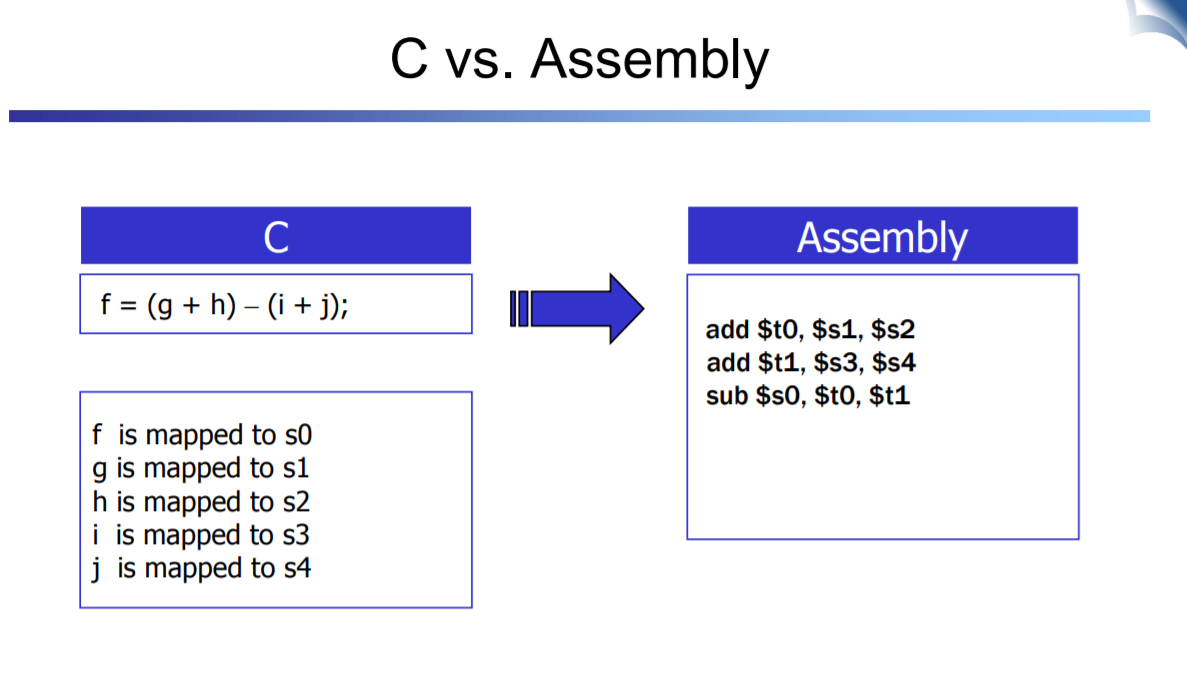

g와 h는 일시적인 값만 의미있기 때문에 temporary 레지스터 사용

배열은 base 주소와 i 만 저장

base address + 4 * i

$t1에 4i를 담는다

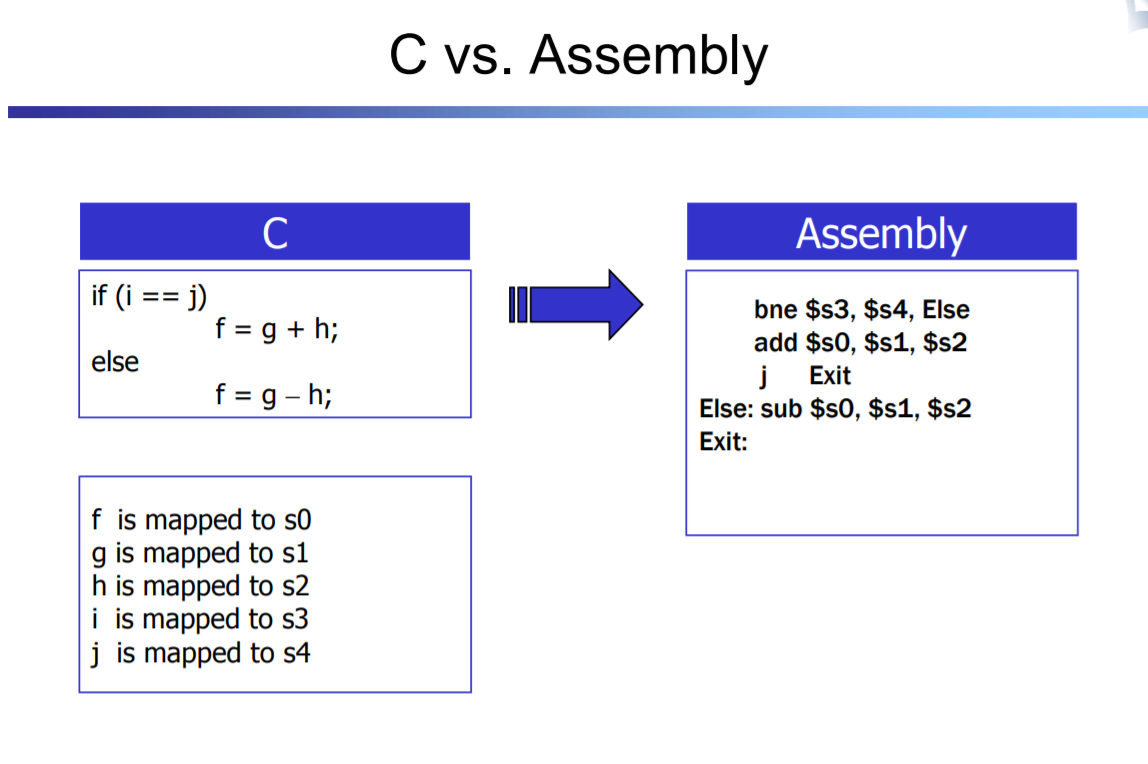

else와 exit은 32bit가 아니지만 컴파일러가 알아서 한다

L0 주소

L1 주소

L2 주소

L3 주소

이런 형식으로 한것을 jump table이라고 한다

실제로 없지만 다음과 같이 입력하게 되면

컴파일러가 알아서 바꿔준다

$s2는 바뀌면 안되고

다음과 같이 바뀌지 말아야 하는것은 안바꾸고

바뀌어야할 값만 건드려야 함

번외

sequential execution에서

exception도 sequantial을 따라야 해서

out of order로 먼저 exception이 발생되었다 해도

그전에 있는 instruction들이 실행되기전까지 exception을 발생시키면 안된다

요약하면 해당 exception전에는 다 실행되어야 하고

뒤에는 전부 실행되지 않았어야 한다

마찬가지로 out of order로 먼저 실행될수도 있지만

레지스터 값을 바꿔야 한다면 바꾸면 안된다

왜냐하면 그전에 있는 instruction이 exception이 날수도 있기 때문이다

'컴퓨터구조,어셈블리어' 카테고리의 다른 글

| Mip (1) 부가적인 내용 (0) | 2020.08.20 |

|---|---|

| Multicycle Implementation (0) | 2020.08.20 |

| Address mode (0) | 2020.08.20 |

| Exception Handling (0) | 2020.05.26 |

| 기본 개념(1) (0) | 2020.05.14 |